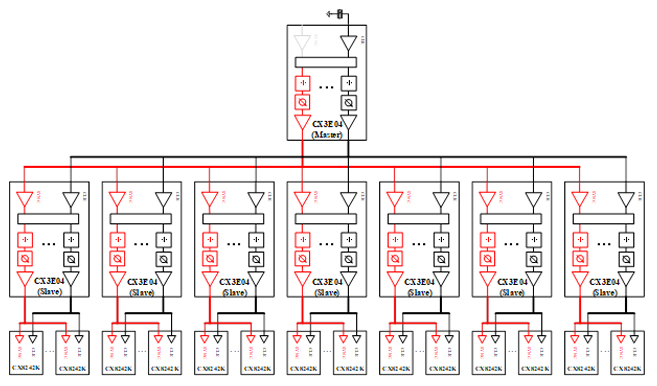

浙江省微波毫米波射频产业联盟旗下杭州城芯科技有限公司随着雷达系统数字化水平的提高,数字相控阵雷达的应用越来越广泛,相较于传统的模拟相控阵雷达系统,数字相控阵雷达系统具有合成波束的灵活性更强、旁辦抑制度更优、动态范围更大等优点。是未来雷达系统的发展方向。相较于传统的模拟相控阵雷达系统,数字相控阵雷达系统不再依靠模拟的移相器、衰减器以及微波合成网络等来实现空间波束的合成与扫描。而是直接通过AD转换器将接收到的模拟信号数字化,在数字域进行更灵活更复杂的数据处理。典型的数字相控阵系统框图如下所示:

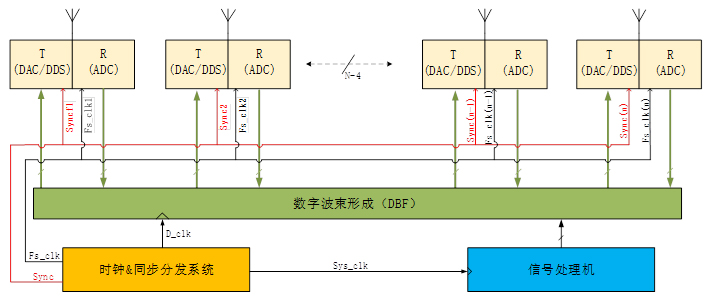

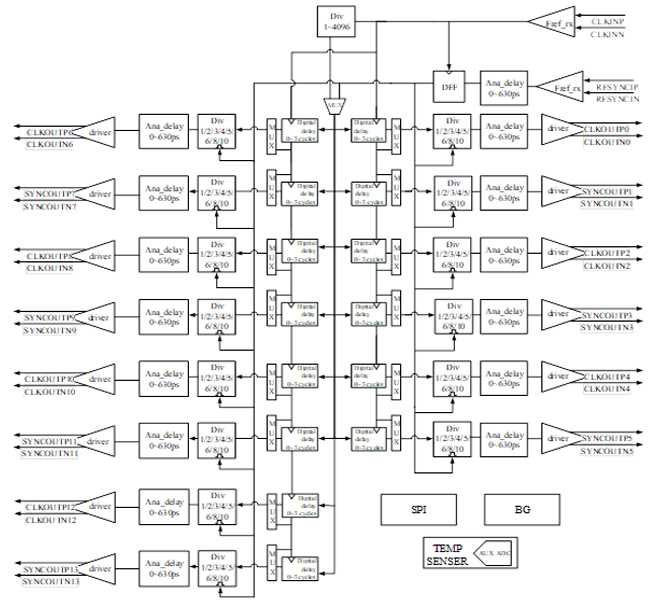

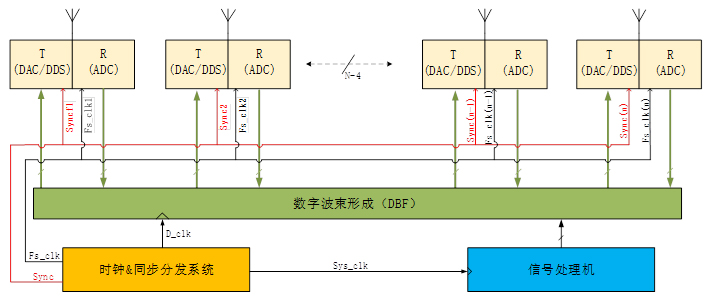

图 1典型数字相控阵系统框图

完整的数字相控阵系统包括数字T/R收发单元阵列(每一个收发单元包括一个接收的ADC模块及一个发射的DAC/DDS模块)、数字波束形成模块(DBF)、信号处理机模块以及时钟生成及分发模块。其中数字收发单元阵列实现模拟信号的收发及数字化,数字波束形成模块通过对各个收发单元的数据进行加权、延时、补偿等操作实现波束的合成,信号处理机模块用于对接收到的数据进行处理并完成对整个系统的控制,时钟生成及分发模块实现采样时钟以及同步信号的分发。

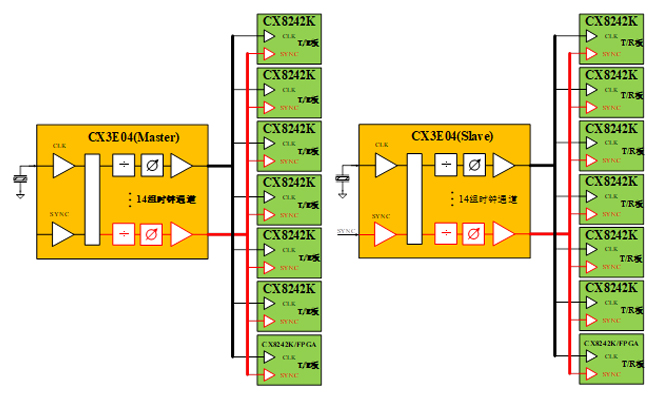

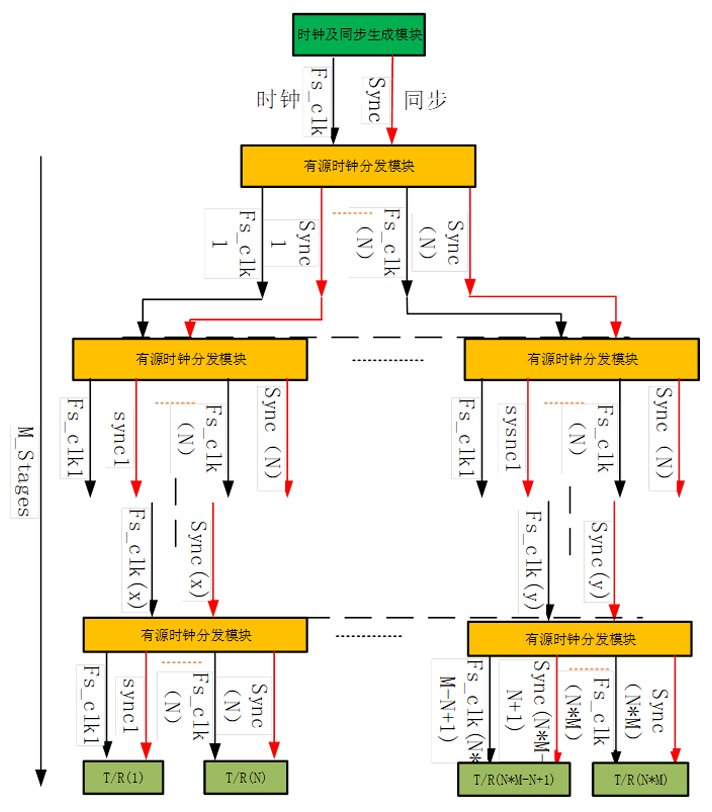

由于数字相控阵系统需要严格控制每个收发单元的采样时刻以方便数字波束合成,故时钟生成及分发模块需要严格约束分发到每一个收发单元的采样时钟(Fs_clk1~Fs_clk(n))的相位关系。理想情况下,需要保证分发到每一个收发单元的采样时钟(Fs_clk1~Fs_clk(n))严格对齐。在大规模数字相控阵系统中,不同的收发单元往往距离很远,且位于不同的PCB板上。为实现同步采样,时钟分发网络一般采用分布式实现以减小连线数量。典型的时钟Fs_clk及同步信号Sync分发网络如图2所示:

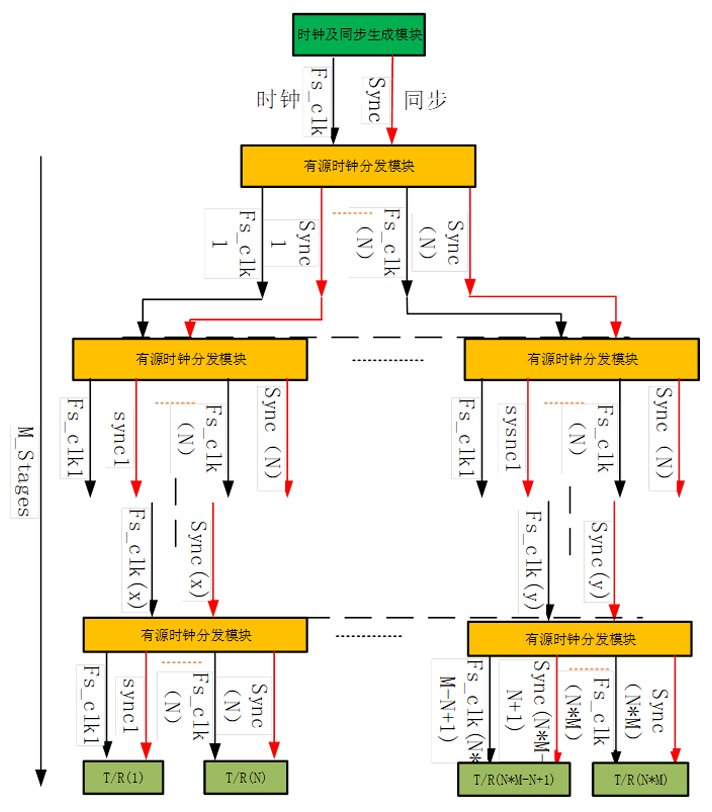

图 2 数字相控阵系统时钟及同步信号分发网络

时钟及同步生成模块产生采样时钟及同步信号,通过有源时钟分发模块将采样时钟及同步信号逐级分发,假设一级有源时钟分发模块可输出N组时钟及同步信号,采用M级串联可实现NM组时钟及同步信号。实际系统实现中由于每一级时钟分发模块及连接电缆均会引入一定的延时Td±Δt,M级模块共引入延时M*(Td±Δt)。其中Td为时钟分发模块的平均绝对延时和电缆的固有延时(相对Fs_clk的延时),Δt为由于模块制造误差及所处环境温度不同造成的延时误差和电缆长度的差异造成的延时。

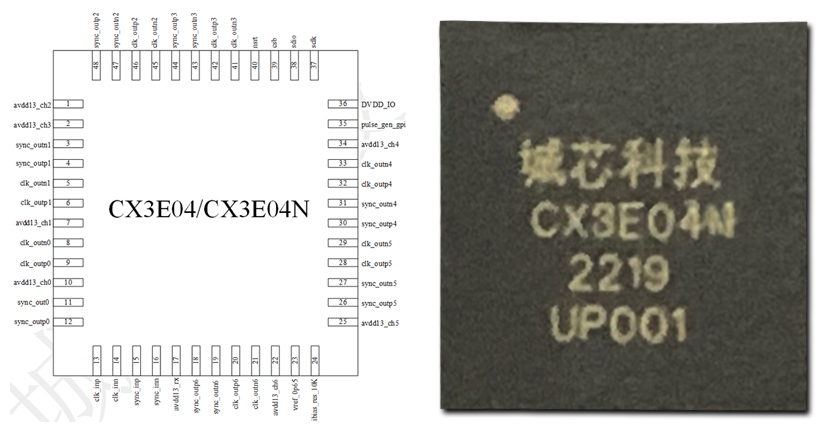

杭州城芯科技有限公司自主研发的CX3E04/CX3E04N芯片,可以为上述时钟和同步的分发系统提供硬件支撑。可极大减小时钟和同步信号分发网络的设计和调试难度。